Introduction

Achieving precise and localized neuronal stimulation is one of the main challenges in neurotechnology. Current approaches often suffer from low spatial specificity, which can lead to unintended activation of surrounding tissue and reduced therapeutic efficiency. A method capable of eliciting spatially localized responses would represent a significant advancement, allowing more targeted interventions, minimizing side effects, and enabling the development of high-resolution neuroprosthetic systems.

Keywords

Brain-Computer Interface (BCI), Visual prosthesis, Lateral geniculate nucleus (LGN),

Neurostimulator, Beamforming, Temporal Interference Stimulation (TIS), Deep brain stimulation

(DBS), Firmware, Neurotechnology, In vitro.

Objective

The objective of this master’s thesis is to design, implement, and verify in vitro the control firmware for a neurostimulator capable of producing localized neuronal responses. This work is framed within the VISNE project, which seeks to advance thalamic visual prostheses. The strategy explored combines two advanced stimulation techniques: beamforming and temporal interference stimulation (TIS), both aimed at improving spatial precision and overcoming the low specificity of conventional neurostimulation.

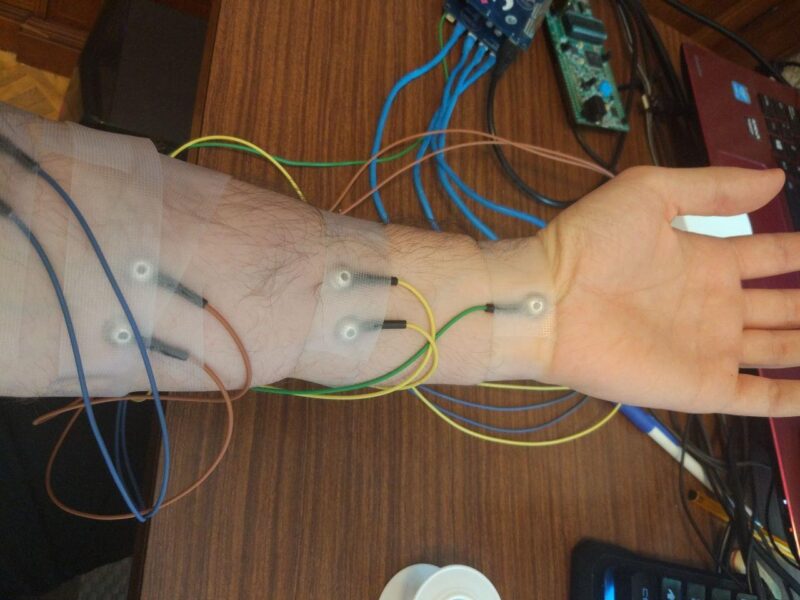

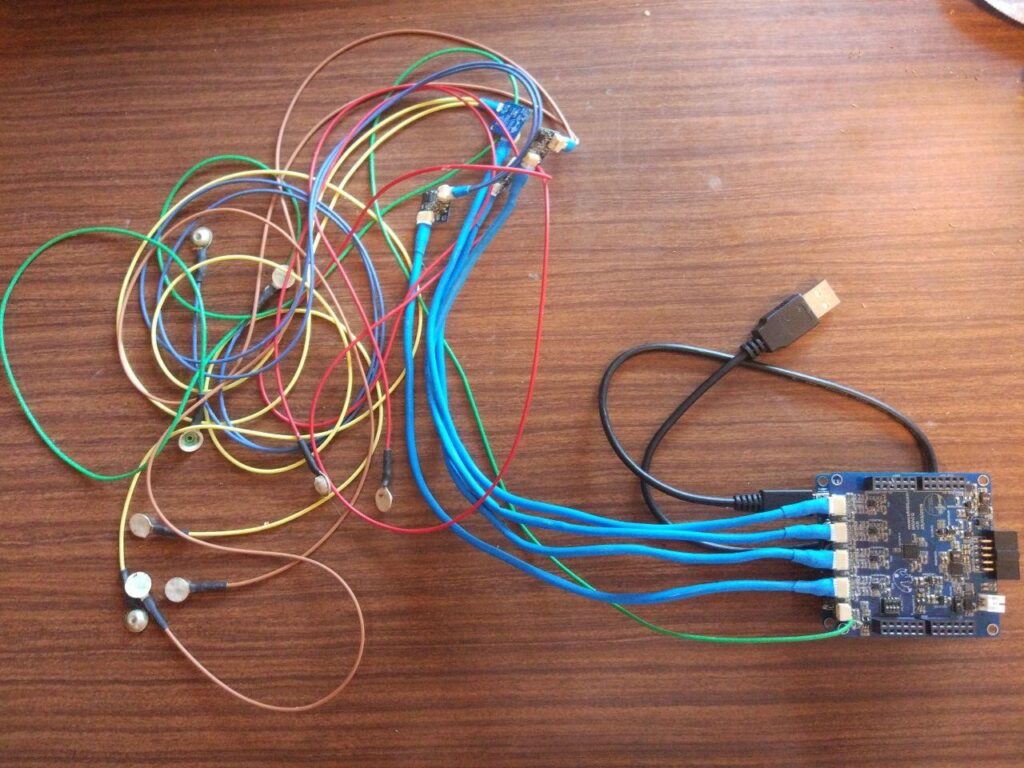

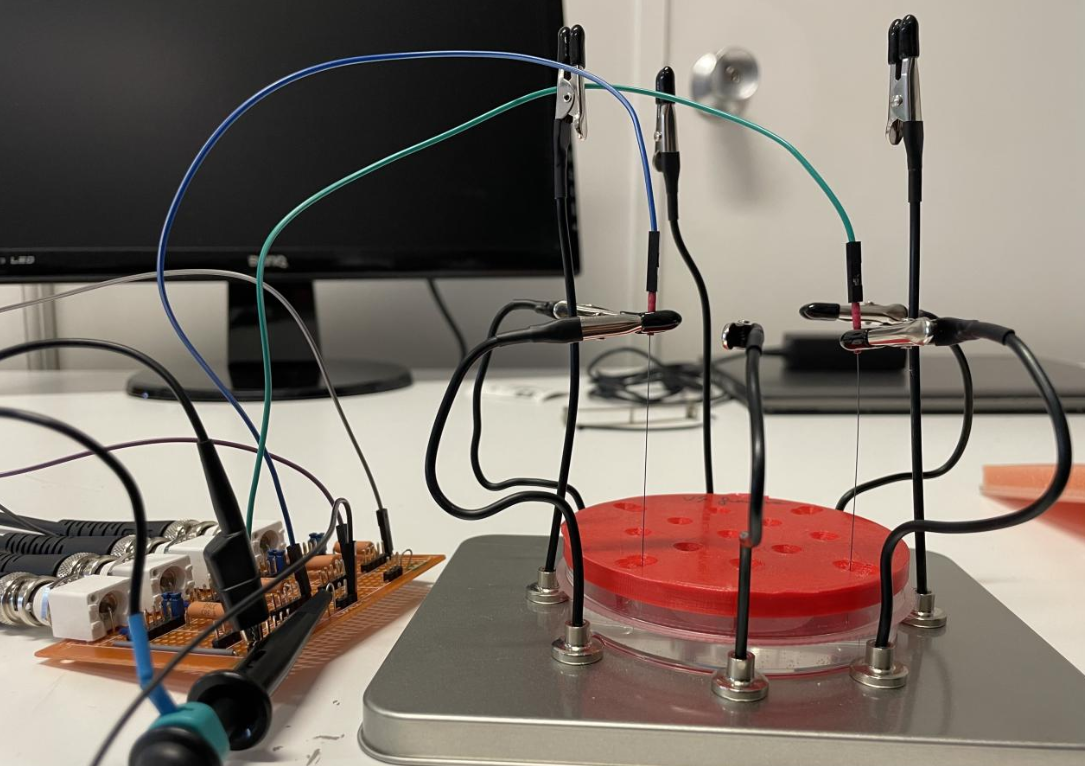

Testing Electrode Setup

Solution

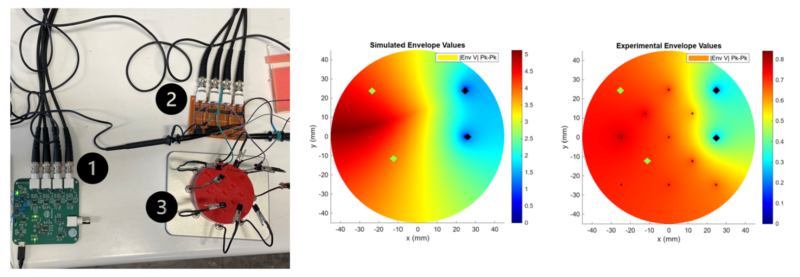

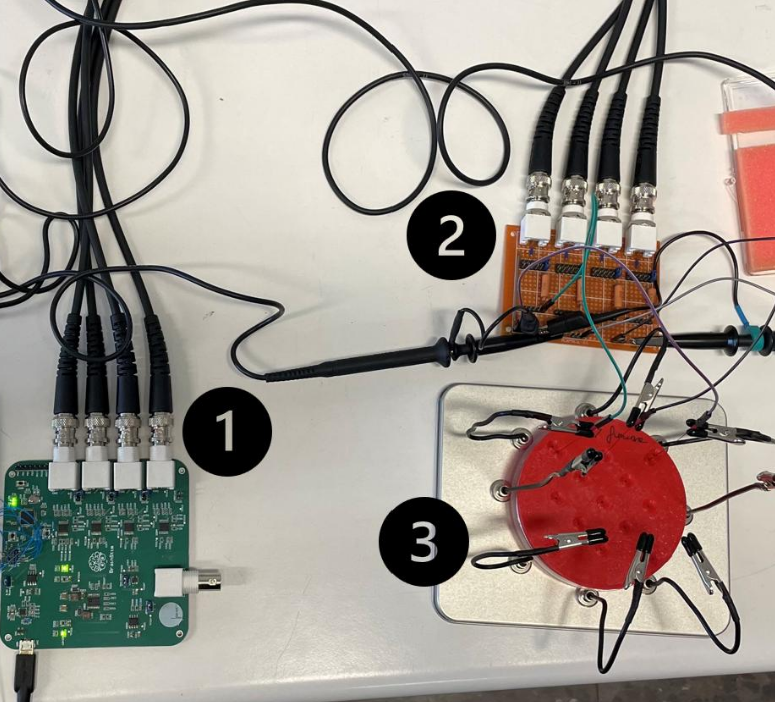

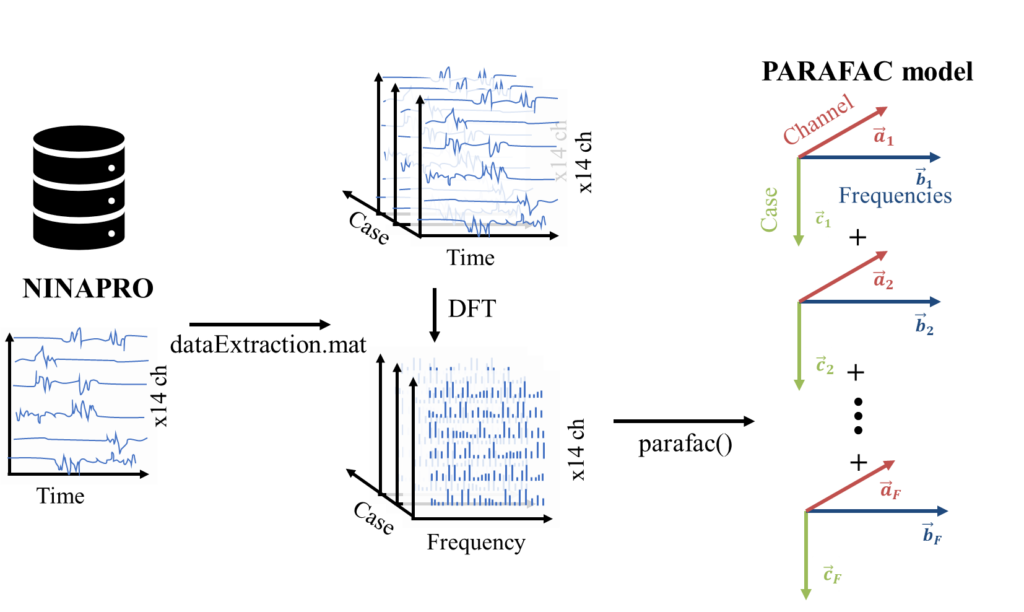

To achieve this, a programmable four-channel neurostimulator was used. The device can generate multiple synchronized waveforms, including biphasic and sinusoidal signals, enabling the shaping of the electric field inside neural tissue. First, computational simulations of beamforming and TIS were performed to predict how stimulation patterns could be steered toward specific regions. Then, in vitro experiments were conducted using the neurostimulator and a custom experimental setup to validate these methods.

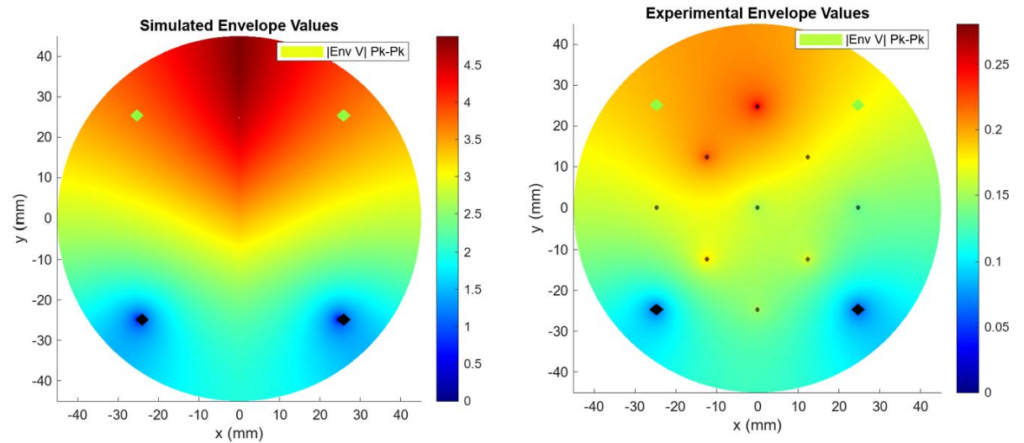

Results

The results showed strong spatial correlations between simulations and experimental measurements, confirming that both beamforming and TIS can focus electrical stimulation effectively. However, challenges were found in reproducing field amplitudes with high accuracy, as statistical analyses (MAE, RMSE) revealed residual errors in the measurements. Among the two techniques, TIS proved particularly promising, successfully generating low-frequency interference envelopes with strong spatial selectivity.