On November 12th, our lab member Roberto Rodriguez Zurrunero defended his PhD Thesis entitled “Dynamic Management in Operating Systems to Improve Energy Efficiency of Resource-Constrained and Wireless Devices”. This work was carried out at B105 Electronic Systems Lab under the direction of Professor Alvaro Araujo.

The thesis defense took place at the ETSI Telecomunicación in Madrid, and the work was evaluated positively earning the highest possible grade, along with the “cum laude” and international mentions.The main contributions of this PhD thesis are the following:

- A proof of concept was designed and implemented to introduce a game theory algorithm in the OS scheduler meant to extend devices’ batteries lifetime.

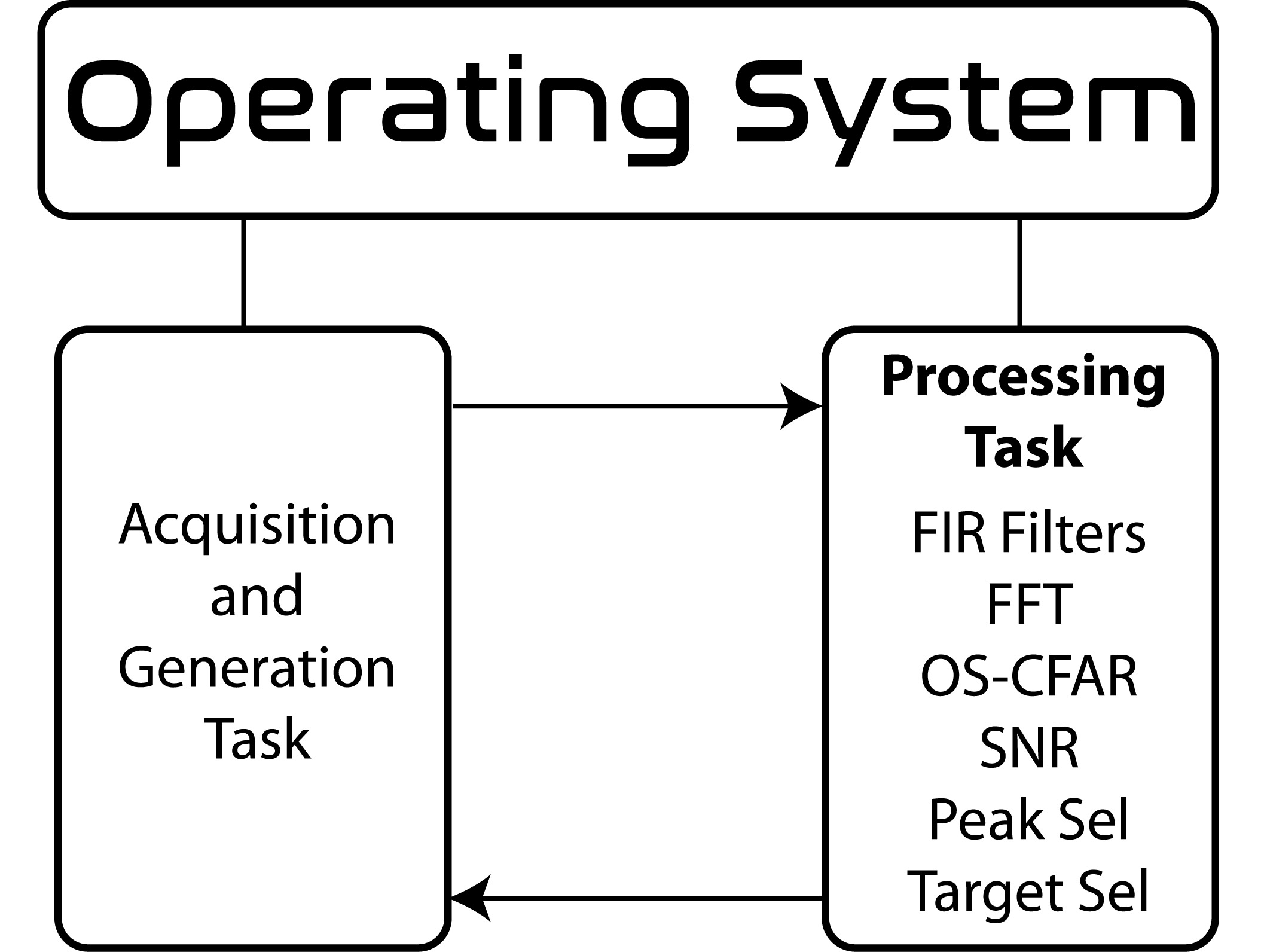

- An OS for resource-constrained devices, YetiOS, was proposed, whose main novel contribution is an adaptive engine that enhances OS’s dynamic capabilities.

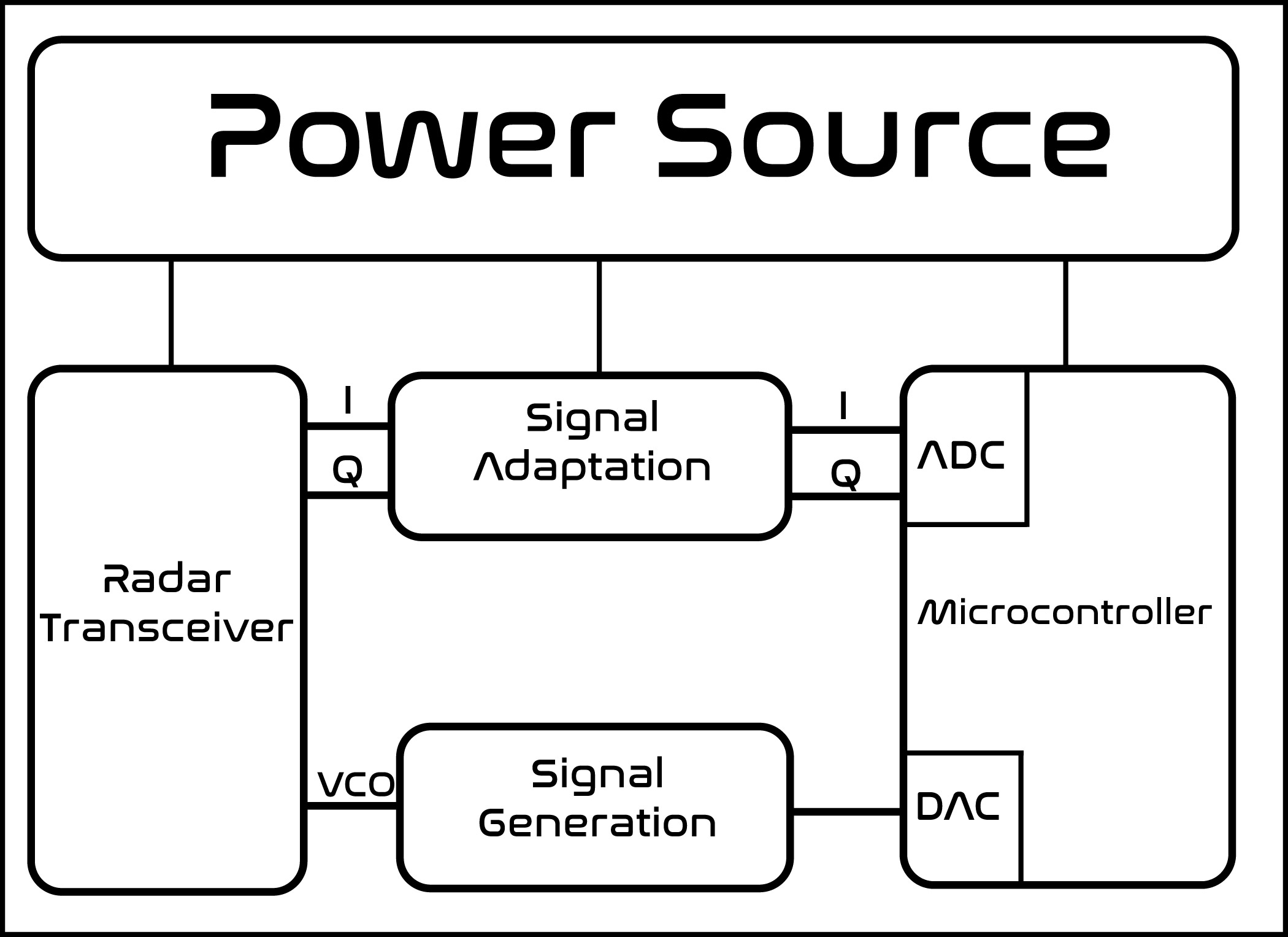

- A study of the cross-influences between the processing and communication tasks in an OS for resource-constrained devices was developed.

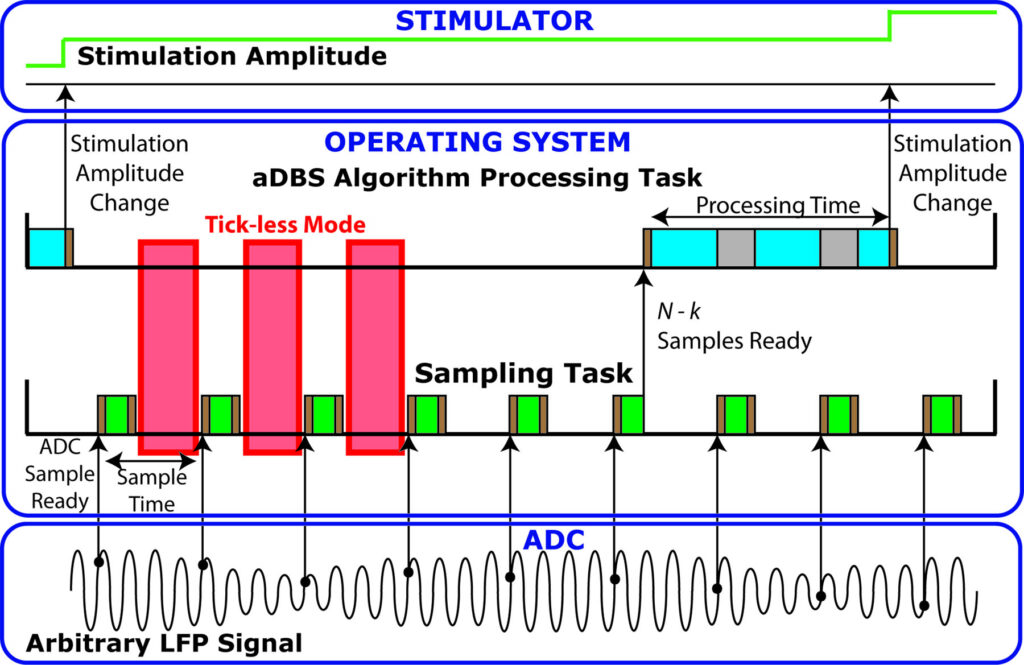

- The use of an OS is introduced for a specific medical application, deep brain stimulation (DBS) devices. Four methods were proposed to reduce the power consumption overhead when introducing an OS in such devices.

- It was demonstrated that in most recent resource-constrained devices with enhanced low power modes (which are used by certain OSes’ power management modules), a lower clock frequency does not necessarily imply a lower power consumption (contrary to what was stated to date in the literature). Therefore, a novel adaptive frequency-scaling algorithm (based on a well-known machine learning algorithm) was proposed to dynamically change the clock frequency to the best value in terms of power consumption.

And, finally, this is the list of peer-reviewed journal and conference publications that were obtained during the course of this PhD:

International journal articles:

- R. Rodriguez-Zurrunero and A. Araujo, “Adaptive frequency scaling strategy to improve energy efficiency in a tick-less Operating System for resource-constrained embedded devices,” Future Generation Computer Systems, vol. 124, pp. 230-242, 2021.

- R. Rodriguez-Zurrunero, A. Araujo, and M. M. Lowery, “Methods for Lowering the Power Consumption of OS-Based Adaptive Deep Brain Stimulation Controllers,” Sensors, vol. 21, iss. 7, 2021.

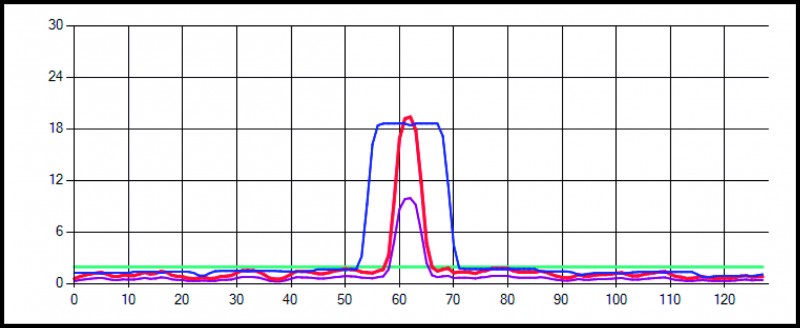

- R. Rodriguez-Zurrunero, R. Utrilla, A. Rozas, and A. Araujo, “Process Management in IoT Operating Systems: Cross-Influence between Processing and Communication Tasks in End-Devices,” Sensors, vol. 19, iss. 4, 2019.

- R. Pita, R. Utrilla, R. Rodriguez-Zurrunero, and A. Araujo, “Experimental Evaluation of an RSSI-Based Localization Algorithm on IoT End-Devices,” Sensors, vol. 19, iss. 18, 2019.

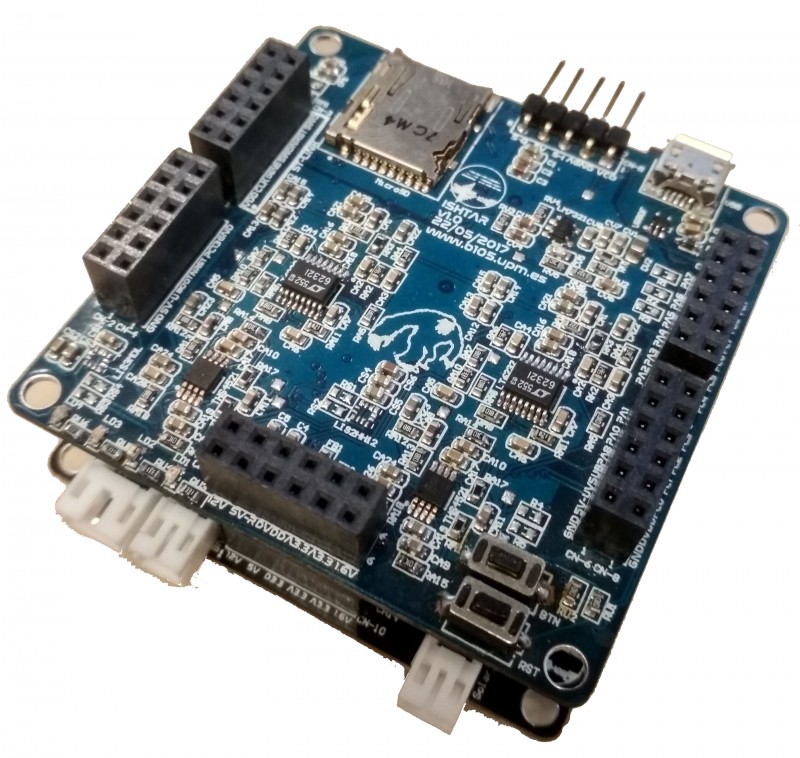

- R. Utrilla, R. Rodriguez-Zurrunero, J. Martin, A. Rozas, and A. Araujo, “MIGOU: A Low-Power Experimental Platform with Programmable Logic Resources and Software-Defined Radio Capabilities,” Sensors, vol. 19, iss. 22, 2019.

- R. Rodriguez-Zurrunero, R. Utrilla, E. Romero, and A. Araujo, “An Adaptive Scheduler for Real-Time Operating Systems to Extend WSN Nodes Lifetime,” Wireless Communications and Mobile Computing, vol. 2018, 2018.

- G. Mujica, R. Rodriguez-Zurrunero, M. Wilby, J. Portilla, A. B. R. González, A. Araujo, T. Riesgo, and J. J. V. Díaz, “Edge and Fog Computing Platform for Data Fusion of Complex Heterogeneous Sensors,” Sensors, vol. 18, iss. 11, 2018.

International conference proceedings:

- R. Rodriguez-Zurrunero, F. Tirado-Andres, and A. Araujo, “YetiOS: an Adaptive Operating System for Wireless Sensor Networks,” in 2018 IEEE 43rd Conference on Local Computer Networks Workshops (LCN Workshops), 2018, pp. 16-22.